rrisc

At Christmas 2020, I decided to hack on my RRISC CPU. Read all about it here.

In a hurry? See it executing a single instruction here, a complete program here, and in physical form here.

- Background and why I built the RRISC CPU

- Radical RISC from the early nineties

- What’s unique about the RRISC CPU

- It’s executing its first instruction

- RRISC Assembly - introduction

- RRISC Assembler - writing programs

- It runs the whole test program

- We have an ALU!

- Playing with the ALU

- Open source, text-based VHDL design: vim, tmux, ghdl, gtkwave

- The FPGA

- NEW Becoming real: The CPU in action on an FPGA board

This is a work in progess. More info on the minimalistic RRISC CPU will follow as soon as I get to it.

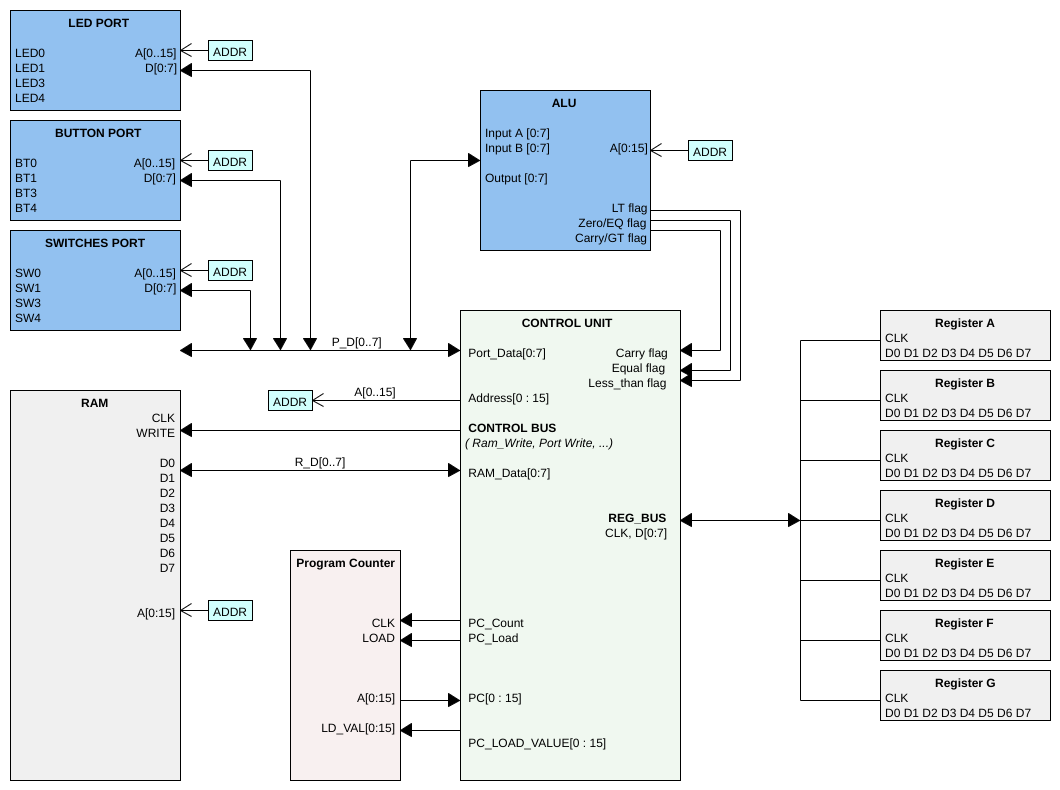

Here is a block diagram of the CPU with periphery of the demo implementation to get you started:

The code is organized as follows:

- asm - contains the assembler and both simtest.asm and testalu.asm which are used for first tests of the CPU

- ghdl - contains the -> ghdl testbench scripts: make and run tests

- project_2.srcs - contains the VHDL CPU and testbench sources. It’s in Vivado style folders. But free ghdl can be used for simulations, Vivado is only required for programming your FPGA.